Volume 8, No. 5, May-June 2017

International Journal of Advanced Research in Computer Science

**RESEARCH PAPER**

## Available Online at www.ijarcs.info

# Improving the Performance of Single Core Processor using FPGA's

Mr. M.S.Satyanarayana Research Scholar, Dept. of CS&E, Sri Venkateshwara College of Engineering, Bangalore -562 157, India Ms. Aruna T M Assistant Professor, Dept. of IS&E, Sri Venkateshwara College of Engineering, Bangalore -562 157, India

Ms. Divya Raj G N Assistant Professor, Dept. of IS&E, Sri Venkateshwara College of Engineering, Bangalore -562 157, India

*Abstract:* Multicore Architecture is a Buzz Word in IT Industry. Multicore made revolutionary changes in the Field of Hardware. Though there is no much usage of newly introduced architectures as we are still using sequential programs for developing software's. But the changes made people to go with new architectures though they are not able to use them completely. In this paper we are going to introduce a mechanism where the single core architecture CPU can be migrated by using FPGAs to cope up with the performance of Multicore Architecture CPU's. The main advantage of this mechanism is that instead of buying Multicore architectures CPU one can use existing CPU with additional functionalities as per their needs. Intern it will make normal users to use existing hardware instead of going for advanced architectures. The main advantage of this mechanism is reducing the cost of hardware instead of buying whenever there is a new version in the market. As per Moore's Law the Number of Transistors on chip will increase every 18 months. Which will make manufacturing companies to release new hardware might not be for 18 months at least for 24 months once. Because of which the users in Developing countries like India are facing problems in buying new hardware on Yearly Basis.

Keywords: Single Core, Multi Core, FPGA

# I. INTRODUCTION

The main objective of this research paper is to make use of existing hardware instead

Of buying new hardware whenever there is a hardware release with minimum changes. And on the other hand it also supports "Green Computing".

Green Computing is defined as reducing the hardware wastage by adopting alternate methods. This research will support Green Computing by making use of Existing Hardware with minimal modifications instead of buying new hardware.

This research has been done on Intel Pentium P4 System which has the clock speed of 3.2 GHZ; though the clock speed is good in this CPU it is a Single Core Processor. That means it is not possible to perform parallel processing.

When there is set of sequential operations need to be executed though it is pretty old processor it is a good option to go with. And the processors are keep on changing from single core to multi core, Quad Core, Octal Core[1] etc...still the utilization of hardware is not up to the mark as we are still writing the sequential programs. To give an example take developing countries like India the main research should start at education level, though India is producing maximum number of engineers every year and as per requirement the educational institutions are keep on changing the Hardware but still all the programs practiced and researched here are sequential. Then what is the use of spending that much cost for hardware better the educational institutes can go with P4 or Dual Core processor.

As per the research made by considering Intel Pentium 4, the performance of single core system is much better than Multicore systems when performing sequential operations.

# **II. EASE OF USE**

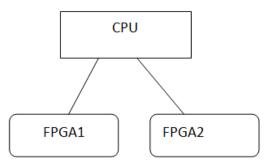

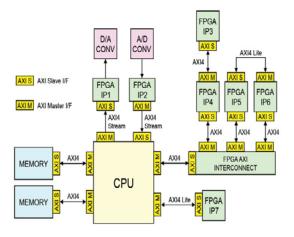

The proposed research is mainly focused on migrating single core architecture processor to multi core architecture processor by connecting FPGA's to the existing processor. In this research the FPGA's[2] are connected to Intel Pentium 4 processor. Though it may not be equally compared with multi core architecture processor, the performance of single core systems will be increased extensively when compared to the existing architecture.

In this proposed system the use of FPGA's made all Single Core Processors to Cope Up with the speed of Multi Core processors. FPGA is nothing but Field Programmable Gate Array. As name indicates it is going to perform set of operations based on the need of users. In this system multiple FPGA's are inter connected with single core CPU to perform multiple tasks.

Any operation which comes to CPU will be verified whether it is an sequential or parallel operation, based on type of operation it will be either redirected to FPGA's or it will be performed directly in Single Core CPU[2]. Most of the operations of any CPU either single or multiple, they are basically classified into Arithmetic or Logical Operations. So, the FPGA's are preloaded with these types of operations required to convert Single Core Processor to Multicore to perform these activities. FPGA's has been given high preference in this system.

So, basically the idea behind the proposed system is migrating single architecture system to Multicore architecture without disturbing the existing hardware.

## **III. METHODOLOGY OF PROPOSED SYSTEM**

In this proposed research, the Intel Pentium 4 System has been taken as the sample single core processor in order to implement proposed system[3].

Initially the P4 system [4] is tested for Benchmark programs and the execution time is noted down for the same. And as mentioned though it is a P4 system it has very good clock speed approximately of 3.2GHZ. The execution time of Benchmark programs has been recorded for comparative study.

Once the Performance of P4 system performance [7] has been done. The FPGA's are connected to system by assigning individual operations to each and every FPGA, as shown in the below figure.

Fig 2: Architecture of CPU after connecting FPGA's Again the Benchmark programs are executed on the same machine. Initially there are so many hurdles in controlling and knowing which FPGA is getting processed for which operation [9]. Later the parallel programming is written and started executing each and every FPGA individually for every single Operation. And the benchmark programs are executed and noted down the results.

# **IV. COMPARATIVE STUDY**

After executing benchmark programs using FPGA's and without using FPGA's, the result found that there is a change in execution time. Though there is no drastic change still the performance is increased. Now the work is going on by interconnecting FPGA's in different order to get better results.

This system is mainly tested for the Quick Sort [8] program by considering it as Benchmark Program.

When the program executed the execution time is as shown in table.

| S.No | Benchmark<br>Program | Processor<br>Type                   | Execution<br>Time |

|------|----------------------|-------------------------------------|-------------------|

| 1    | Quick Sort           | Normal P4<br>Processor              | 0.32 Sec          |

| 2.   | Quick Sort           | P4<br>processor<br>with 2<br>FPGA's | 0.027Sec          |

| S.No | Benchmark<br>Program | Processor<br>Type                   | Execution<br>Time |

|------|----------------------|-------------------------------------|-------------------|

| 1    | Quick Sort           | Normal P4<br>Processor              | 0.32 Sec          |

| 2.   | Quick Sort           | P4<br>processor<br>with 2<br>FPGA's | 0.027Sec          |

| 3.   | Quick Sort           | Multicore<br>System                 | 0.19 Sec          |

After doing research by considering different benchmark programs [5], the result found that there is still some gap between the proposed system and the original Multicore system [6].

The research is still going on by replacing and writing much simpler parallel programs in each and every FPGA.

### V. CONCLUSION

This proposed system may be one of the best solutions for the people who want to use high performance system without buying new hardware every time whenever there is a minimal change in the hardware.

And this proposed system really makes revolutionary changes in the field of Hardware. And initiation of Green Computing with reference to new hardware has been solved with system.

### VI. FUTURE ENHANCEMENT

In future the system may be developed such a way that the FPGA's are effectively used to improve the performance of single core system and also the execution time of the this system may be much better than the original Multicore system. And this system may be one of the ways to implement Green Computing which is latest trend in IT.

In future also there is a possibility that FPGA's may get replaced with any of the new technologies like ASIC with few modifications.

### REFERENCES

- S. M. Alnaeli, A. Alali, J. I. Maletic, "Empirically Examining the Parallelizability of Open Source Software System", Reverse Engineering (WCRE) 2012 19th Working Conference on, pp. 377-386, 2012.

- [2] C. Iancu, S. Hofmeyr, F. Blagojevic, Z. Yili, "Oversubscription on multicore processors", Parallel & Distributed Processing (IPDPS) 2010 IEEE International Symposium on, pp. 1-11, 2010.

- [3] Z. Yuanfang, C. Gill, L. Chenyang, "Real-Time Performance and Middleware for Multiprocessor and Multicore Linux Platforms", Embedded and Real-Time Computing Systems and Applications 2009. RTCSA '09. 15th IEEE International Conference on, pp. 437-446, 2009

- [4] L. Chai, A. Hartono, and D. K. Panda. Designing High PerformanceandScalableMPIIntra-

nodeCommunicationSupport for Clusters. In The IEEE International Conference on Cluster Computing, 2006.

- [5] Max Domeika and Lerie Kane. Optimization Techniques for Intel Multi-Core Processors. http://www3.intel.com/cd/ids/developer/asmona/eng/261221. htm?page=1.

- [6] D.H.Baileyetal. TheNASparallelbenchmarks. volume 5, pages 63–73, Fall1991.

- [7] Matthew Curtis-Maury et al. An Evaluation of OpenMP on Current and Emerging Multithreaded/Multicore Processors. In IWOMP,2005.

- [8] Sadaf R. Alam et al. Characterization fif Scienti Workloads on Systems with Multi-Core Processors. In International Symposium on Workload Characterization, 2006.

- [9] P. Kongetira, K. Aingaran, K. Olukotun, "Niagara: A 32-way multithreaded Sparc processor", Proc. IEEE Micro, vol. 25, no. 2, pp. 21-29, Mar. 2005